Introduction

ScanImage 5 Galvo/Galvo will support a combination of a variety of legacy DAQ boards for simultaneous sampling. Since not all supported boards are equipped with a sufficient amount of analog outputs for mirror and beam control, SI5 will be able to combine multiple devices to provide the required functionality. In contrast to SI5 resonant, SI5 galvo/galvo is a strictly deterministic system. This means that the timely behavior of SI5 galvo/galvo is predictable (in SI5 resonant, the heartbeat of the system is the period clock, which jitters)

To maintain the determinism of the system while using multiple DAQ boards, the boards must be synchronized to each other. Due to the variety of the supported board generations, only one synchronization technique is suitable (see discussion below).

The current specification of SI5 galvo/galvo includes support for the following hardware configurations

- PCI-6110, plus PCIe-6321 or higher for beam(s) (for legacy users)

- PCI 6132/6133 plus PCIe-6323 for galvo plus beam(s). 6321 ok if no beams; 6323 + 6321 if 3 beams.

- Pure X series - either USB or PXIe 6356 for acq & galvos; plus 6321 or higher board for beam(s)

Trigger Methods

1. use a common timebase + shared start trigger between multiple

Description: X series board can export a 10MHz reference clock. One board acts as the timebase master, the other boards import the 10MHz clock and phase lock their internal 100MHz oscillator. Now, synchronized tasks can be started by sharing a common start trigger.

Disadvantage: two wires are needed to sync multiple devices with each other (start trigger + reference clock)

Problem: In SI5 Galvo/Galvo a mix between X-Series and S-Series boards is used. While the X-Series boards support importing/exporting reference clocks, the S-Series does not.

2. use the 20MHz timebase + shared start trigger between S-Series and X-Series

Description: the S-Series allows to export/import its 20MHz timebase, the X-Series can export its 20MHz timebase or set up its tasks to use an external timebase. sharing the timebases + a shared trigger allows synchronization of tasks across boards.

Disadvantages:

- two wires are needed to sync multiple devices with each other (start trigger + 20MHz timebase)

- to export / import the 20MHz timebase on the S-series, only certain PFI/RTSI lines are allowed

- to export the 20MHz timebase on the X-series a counter is needed for signal routing

Problem: National Instruments does not recommend to share digital signals of 20MHz or higher via PFI/RTSI/PXI -Trigger lines due to possible signal degradation. (this is the reason why the X-serie's reference clock is only 10MHz)

3. use a counter on the X-series to generate the S-series sample clock

Description: the X-series is equipped with 4 counters. use one of them to generate the S-series sample clock (typically 1.25MHz). The S-series board is then clock slave to the X-series board, which takes care of triggering and starting/stopping the acquisition.

Advantage: only one connection is needed between X-Series and S-series board, 1.25MHz signal is safe to export over PFI trigger lines

Discussion

Because options 1 and 2 are not suitable due to functional / electrical limitations of the boards, option 3 is chosen as the synchronization method between S-series and X-series DAQ boards.

If further X-series boards need to be synchronized with the base system, the reference clock of the existing timebase master X-series board can be used.

Implementation

In the configuration three boards types will be configurable:

- acquisition board (analog input for PMT sampling)

- controller board (analog outputs for XY galvo control)

- auxiliary board (X-series board for clock generation (acq clock, frame clock, line clock, pixel clock)

The assignment of devices to the board types is not mutually exclusive. The only limitations are:

- the acquisition board must support simultaneous sampling

- the controller board must be either the same as the acquisition board or to the auxiliary board

- the auxiliary board must be an X-series board

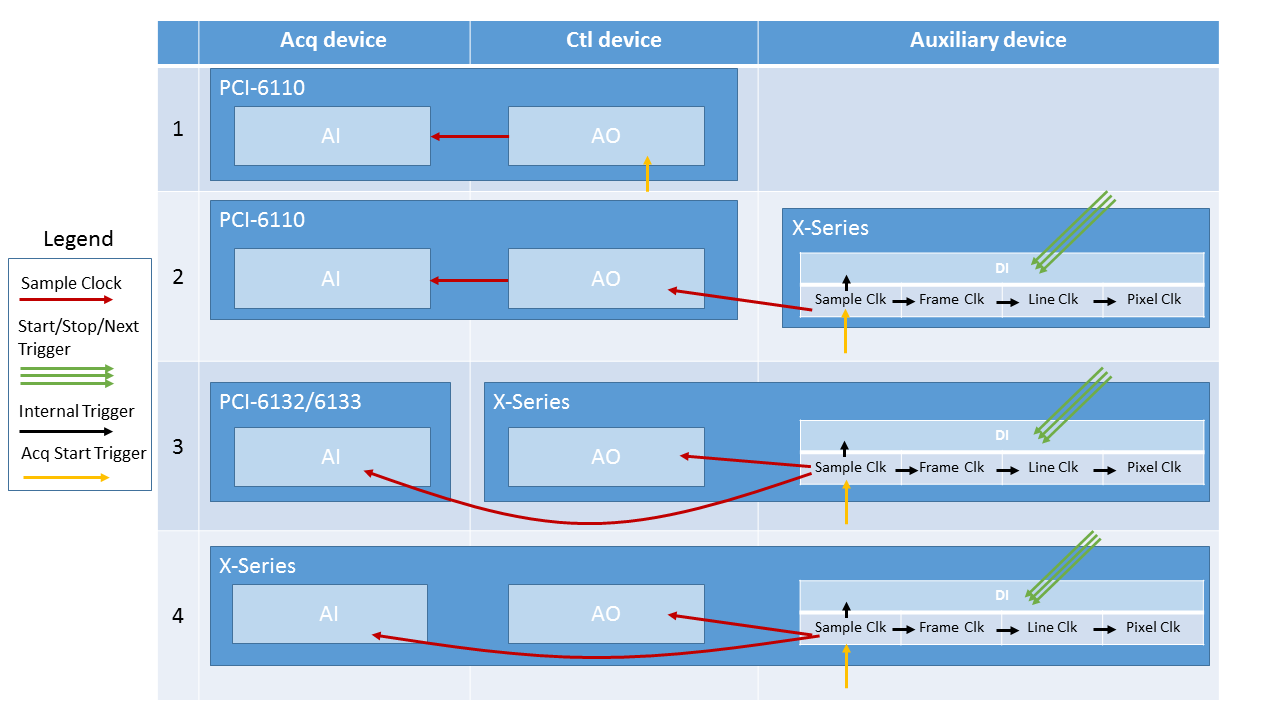

Four possible configurations are achievable:

1: one device hosts AI and AO tasks for XY Galvo control (e.g. PCI-6110, 'Dev1'):

deviceNameAcq = 'Dev1'; deviceNameGalvo = 'Dev1'; deviceNameAux = '';

Note: While it is possible to run SI5 Galvo/Galvo without an auxiliary device, the following functionality will be unavailable:

- frame/line/pixel clock export

- trigger timestamping

- next/stop triggering

- synchronization with other DAQ hardware

2: one board hosts AI and AO tasks for XY Galvo control (e.g. PCI-6110, 'Dev1'), and one X-series auxiliary board ('Dev2') is used to generate clocks.

deviceNameAcq = 'Dev1'; deviceNameGalvo = 'Dev1'; deviceNameAux = 'Dev2';

3: one board hosts the AI task (e.g. PCI-6132, 'Dev1', no AOs available), and one X-series auxiliary board ('Dev2') is used to generate clocks + AO XY galvo control signals

deviceNameAcq = 'Dev1'; deviceNameGalvo = 'Dev2'; deviceNameAux = 'Dev2';

4: one simultaneously sampled X-series (e.g. 6356, 'Dev1') is used for all inputs/outputs

deviceNameAcq = 'Dev1'; deviceNameGalvo = 'Dev1'; deviceNameAux = 'Dev1';

In order to implement the synchronization, the auxiliary board (if present) uses one counter to generate the 1.25MHz sample clock of the digitizer board. The following graphic displays the described board combinations: